# Rudraksh: A compact and lightweight post-quantum key-encapsulation mechanism

Suparna Kundu<sup>1</sup>, Archisman Ghosh<sup>2</sup>, Angshuman Karmakar<sup>3</sup>, Shreyas Sen<sup>2</sup> and Ingrid Verbauwhede<sup>1</sup>

<sup>1</sup> COSIC, KU Leuven, Belgium

<sup>2</sup> Purdue University, USA

<sup>3</sup> Indian Institute of Technology Kanpur, India

suparna.kundu@esat.kuleuven.be, ghosh69@purdue.edu, angshuman@cse.iitk.ac.in,

shreyas@purdue.edu, ingrid.verbauwhede@esat.kuleuven.be

**Abstract.** Resource-constrained devices such as wireless sensors and Internet of Things (IoT) devices have become ubiquitous in our digital ecosystem. These devices generate and handle a major part of our digital data. However, due to the impending threat of quantum computers on our existing public-key cryptographic schemes and the limited resources available on IoT devices, it is important to design lightweight post-quantum cryptographic (PQC) schemes suitable for these devices.

In this work, we explored the design space of learning with error-based PQC schemes to design a lightweight key-encapsulation mechanism (KEM) suitable for resourceconstrained devices. We have done a scrupulous and extensive analysis and evaluation of different design elements, such as polynomial size, field modulus structure, reduction algorithm, and secret and error distribution of an LWE-based KEM. Our explorations led to the proposal of a lightweight PQC-KEM, Rudraksh, without compromising security. Our scheme provides security against chosen ciphertext attacks (CCA) with more than 100 bits of Core-SVP post-quantum security and belongs to the NIST-level-I security category (provide security at least as much as AES-128). We have also shown how ASCON can be used for lightweight pseudo-random number generation and hash function in the lattice-based KEMs instead of the widely used Keccak for lightweight design. Our FPGA results show that Rudraksh currently requires the least area among the PQC KEMs of similar security. Our implementation of Rudraksh provides a  $\sim 3 \times$ improvement in terms of the area requirement compared to the state-of-the-art areaoptimized implementation of Kyber, can operate at 63%-76% higher frequency with respect to high-throughput Kyber, and improves time-area-product  $\sim 2 \times$  compared to the state-of-the-art compact implementation of Kyber published in HPEC 2022.

**Keywords:** Post-quantum cryptography, key-encapsulation mechanism, Lightweight cryptography, Lattice-based cryptography, Hardware implementation, FPGA.

### 1 Introduction

Lightweight cryptography (LWC) is a niche research area in cryptography that studies methods to incorporate secure cryptographic protocols into devices with minimal resources due to their operational requirements. There are two major avenues in the research and development of LWC. First, implement existing cryptographic protocols that are not specifically designed as LWC in a *lightweight manner* such as lightweight implementations of symmetric-key ciphers such as AES (Advanced Encryption Standard) [Can05, BMR<sup>+</sup>13], Keccak [KY10, KYS<sup>+</sup>11], or public-key cryptographic (PKC) algorithms such as RSA [RSA78] and elliptic curve cryptography (ECC) [HWF08, BGK<sup>+</sup>06]. Second, design cryptographic schemes that are

lightweight implementation friendly such as symmetric-key cipher ASCON [DEMS12], which is the winner of the National Institute of Standards and Technology's (NIST's) lightweight cryptography competition [NIS23a] and also selected as the 'primary choice' for lightweight authenticated encryption in the final portfolio of the CAESAR [CAE19] competition. Another example is Quark [AHMN13], which is a lightweight hash function designed specifically for low-power devices such as Radio Frequency Identification (RFID) devices.

Recently, NIST also standardized post-quantum cryptography (PQC) schemes in anticipation of the arrival of large-scale quantum computers and their detrimental effect on our existing PKC schemes. These are key-encapsulation mechanism (KEM) CRYSTALS-Kyber [ABD $^+$ 21] and digital signature schemes SPHINCS+ [ABB $^+$ 18], CRYSTALS-Dilithium [DKL $^+$ 18], and Falcon [FHK $^+$ 18]. Naturally, we will also have to equip resource-constrained Internet of Things (IoT) and embedded devices with quantum-secure cryptographic schemes to secure them for the foreseeable future. Although it should be noted that there exist some LW implementations of the standardized schemes such as the compact implementation Kyber [ZLZ $^+$ 22] or Dilithium [ZZW $^+$ 21, LSG21].

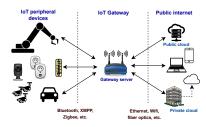

Apart from LW design, there is another subtle issue in incorporating cryptographic schemes into IoT devices. Consider a typical IoT ecosystem, as shown in Fig. 1. Here, the IoT peripheral devices connect to the public internet through an IoT gateway server. The IoT gateway architecture has several layers, such as a security layer, device layer, data management layer, etc. As part of connecting IoT peripheral devices, the IoT gateway servers perform data filtering and processing, protocol translation, authorization and authentication, etc. Whenever a user or device wants to connect to a peripheral device or vice-versa, the gateway servers have to run proper authentication and authorization protocols to make this happen. The gateway servers are usually powerful servers serving numerous IoT peripheral devices simultaneously. So, for them, high throughput is a more important operational metric than resource consumption. Meanwhile, the reverse is more important for IoT peripheral devices, which connect sporadically to the IoT gateway servers. Therefore, a flexible cryptographic scheme that can be instantiated either in a high latency and low resource consumption mode or in a low latency and high resource consumption mode is highly suitable in this scenario.

Figure 1: An illustrative example of a typical IoT gateway architecture.

From a very broad perspective, this work aims to push the lower bound of the resource consumption of post-quantum cryptography, especially learning with errors (LWE)-based post-quantum cryptography. For the rest of this work, we will use the term lattice-based cryptography (LBC) to denote the cryptographic schemes based on the learning with errors (LWE) [Reg09] problem or its variants such as ring-learning with errors [LPR10], learning with rounding [BPR12], etc. We also want to delineate the term lightweight implementation here. For software implementation on resource constraint devices like Cortex-M0/M4 we use the term lightweight implementation for implementations with low memory footprint such as [BKS19, KBRV18, GKS20]. Lightweight design also implies low area and low-power or energy solutions for hardware devices such as field-programmable gate arrays (FPGA) or application-specific integrated circuits (ASIC); however, low-power or energy implementation cannot be demonstrated without custom ASIC design as FPGA defaults

to high power-consuming interfaces. We expect that the ASIC version of our design will also reflect relatively lower memory as we can custom-make memory as per our requirement instead of using entire Block RAMs. We have demonstrated a low-area implementation on FPGA in this work. We have kept ASIC-related optimization as part of future work. Below, we briefly summarize the salient contributions of this work.

PQ KEM suitable for resource-constrained devices: We propose a lightweight post-quantum chosen-ciphertext attack (CCA) secure module-learning with errors-based key-encapsulation mechanism (MLWE-KEM), Rudraksh. In 1998, [HPS98] proposed NTRU-Encrypt, a public-key encryption scheme that can achieve high speed and require low memory. Years later, [BGG<sup>+</sup>16] deliberated on a lightweight CPA-secure LWE-based key-exchange scheme suitable for IoT devices before us. However, none of these schemes are secure under chosen ciphertext attacks. Hermans et al. [HPVP11] have pointed out that a CPA-secure scheme can only provide security against a narrow range of adversaries. Therefore, in this work, we focus on designing a CCA-secure KEM. Kindly note that several CCA-secure NTRUbased KEM have been proposed during the NIST PQC standardization procedure. Most lattice-based KEMs, such as Kyber, Saber [BBD+21] (LightSaber), NewHope [ADPS16], and NTRU-based KEMs [CDH<sup>+</sup>19], have a low-security version design. Still, these are not explicitly designed to be lightweight, specifically for resource-constrained devices. One of the most prominent issues among the standardized PQC signatures is their large signature size compared to the classical signature schemes. This has a very detrimental effect on some protocols, such as transport layer security (TLS), where the increase in the size of certificates in the chain-of-trust model leads to serious performance degradation [SKD20] due to the congestion control mechanism of the transmission control protocol (TCP). To address such problems, NIST has called for another standardization [CML23] for PQ signatures with small signature sizes and fast verification time. In addition, some proposals have been made to replace the TLS handshake with a CCA-secure KEM, such as KEMTLS [SSW20] or TLS-PDK [SSW21], for better performance. Therefore, we believe that lightweight KEMs can profoundly impact the transition from classical PKC to PQC. Further, the techniques developed in this work can also be used to create a lightweight PQ digital signature scheme.

Practical design strategy: We adopt a new design style that is strongly coupled with hardware implementation. Our design decisions have been strongly driven by their potential advantage for lightweight hardware implementation. We explored the parameter space of LWE-based KEMs to propose optimum parameters that satisfy our design objectives. The NIST PQ standardization procedure witnessed a collective effort from researchers around the world for a thorough and rigorous analysis of different design elements of LBC. Therefore, to reap the benefits of the procedure and to bolster confidence in our designed KEM Rudraksh, we have kept the design very Kyber-esque. We refrained from making aggressive design decisions such as using non-constant-time modular reductions. We explore different centered binomial distributions with different variations for sampling error and secret vectors. However, we have not explored other distributions, such as the binary distribution [BGG<sup>+</sup>16] or the fixed weight distribution [BBF<sup>+</sup>19, CCHY23, PJP<sup>+</sup>22]. We also explored and analyzed different implementations of number theoretic transform (NTT)-based polynomial multiplication. We have used a modular reduction algorithm for lightweight hardware implementation. We also provided an optimized hardware implementation using the Xilinx Virtex-7 and Artix-7 FPGA to demonstrate the efficacy and justify our design decisions. We have also extensively compared our scheme with other state-of-the-art compact implementations of LBC.

**Lightweight implementation:** We demonstrated our design of Rudraksh using a lightweight implementation on FPGA. We observe that a major source of hardware overhead for lattice-based KEMs such as Kyber comes mainly from the bulky Keccak [BDPV13] module, storing the twiddle factors for NTT, and other memory requirements. We want to make this KEM design suitable for lightweight CCA-secure KEMs, so we focus on minimizing the area in terms of FPGA resources such as LUT, DSP, flip-flops, and memory with reasonable

latency (54-81  $\mu$ s). ASCON [DEMS12] is a family of lightweight authenticated encryption and hashing algorithms. We have replaced Keccak with ASCON [DEMS12] to reduce the overhead of Keccak. This also demonstrates the efficiency and benefits of using ASCON in a LBC scheme. Our results show that area and memory can be reduced by approximately  $\sim 3\times$  with respect to the most resource-optimized Kyber [HLLM24]. Our pipelined hardware implementation of Rudraksh can operate at 63%-76% higher frequency compared to high-throughput Kyber [DFA+20] and also provides  $\sim 2\times$  time-area-product improvement compared to the compact implementation of Kyber [ZLZ+22].

# 2 Background and related works

We denote the set of integers modulo q as  $\mathbb{Z}_q$  and the quotient ring  $\mathbb{Z}_q/(x^n+1)$  as  $R_q$   $(n \ge 1)$ . The ring containing the vectors with  $\ell$  elements and the matrix with  $\ell \times \ell$  elements from  $R_q$  are represented as  $R_q^{(\ell)}$  and  $R_q^{(\ell imes \ell)}$ , respectively. Lowercase letters indicate polynomials  $(v \in R_q)$ , and bold lowercase letters denote vectors of polynomials  $(\mathbf{s} \in R_q^{(\ell)})$ . Bold uppercase letters represent matrices of polynomials  $(\mathbf{A} \in R_q^{(\ell \times \ell)})$ . Multiplication of two polynomials  $a \in R_q$ and  $b \in R_q$  is denoted by  $a \cdot b \in R_q$ . The number theoretic transform (NTT) representation of a polynomial  $a \in R_q$  is denoted by  $\hat{a}$ . The point-wise multiplication between these two polynomials in the NTT domain  $\hat{a}$  and  $\hat{b}$  is presented by  $(\hat{a} \circ \hat{b})$ . When NTT is applied to each constituent element of  $\mathbf{a} \in R_q^{(\ell)}$  and  $\mathbf{A} \in R_q^{(\ell \times \ell)}$ , it is denoted as  $\hat{\mathbf{a}}$  and  $\hat{\mathbf{A}}$  respectively.  $\hat{\mathbf{a}} \circ \hat{\mathbf{b}}$ represents vector-vector point-wise multiplication between vector of polynomials  $\hat{\boldsymbol{a}}$  and vector of polynomials  $\hat{b}$ .  $\hat{A} \circ \hat{b}$  denotes matrix-vector point-wise multiplication (PWM) between a matrix of polynomials  $\hat{\boldsymbol{A}}$  and a vector of polynomials  $\hat{\boldsymbol{b}}$ .  $a \leftarrow \chi(S)$  represents that a is sampled from the set S according to the distribution  $\chi$ , and we use  $\leftarrow$  to denote probabilistic output.  $a := \chi(S; \operatorname{seed}_a)$  indicates that  $a \in S$  is generated from the  $\operatorname{seed}_a$  and follows the distribution  $\chi$ , and we use := to denote deterministic output. We use  $\mathcal{U}$  to denote uniform distribution and  $\beta_{\mu}$  to denote the centered binomial distribution (CBD) with standard deviation  $\sqrt{\mu/2}$ . We denote the Hamming weight function by HW. |x| denotes bit length of the bitstring x.

# 2.1 Learning with Errors Problem

The learning with errors (LWE) problem was introduced by Regev [Reg09] and is as hard as standard worst-case lattice problems [Pei09]. Given  $\mathbf{A} \leftarrow \mathcal{U}(\mathbb{Z}_q^{(m \times n)})$ ,  $m = O(\operatorname{poly}(n))$   $\mathbf{s} \leftarrow \chi_1(\mathbb{Z}_q^{(n)})$ , and  $\mathbf{e} \leftarrow \chi_2(\mathbb{Z}_q^{(m)})$ , where  $\chi_1$  and  $\chi_2$  are two narrow distributions. The LWE instance consists of the pair  $(\mathbf{A}, \mathbf{A} \cdot \mathbf{s} + \mathbf{e}) \in \mathbb{Z}_q^{(m \times n)} \times \mathbb{Z}_q^{(m)}$ . The LWE problem states that for  $b \leftarrow \mathcal{U}(\mathbb{Z}_q^{(m)})$ , it is hard to distinguish between the pairs  $(\mathbf{A}, \mathbf{A} \cdot \mathbf{s} + \mathbf{e})$  and  $(\mathbf{A}, \mathbf{b})$ . The hardness depends on the distributions  $\chi_1, \chi_2$  and the parameters q, n. The Ring-LWE (RLWE) [LPR10] and the Module-LWE (MLWE) [LS15] problems are algebraically structured variants of the LWE problem.  $\mathbf{A}, \mathbf{s}, \mathbf{e}$  are polynomials sampled from the ring  $R_q = \mathbb{Z}_q/(x^n+1)$  in the RLWE problem. In the MLWE problem,  $\mathbf{A}$  is a matrix of polynomials sampled uniformly from  $R_q^{(\ell \times \ell)}$ , and  $\mathbf{s}, \mathbf{e}$  are vectors of polynomials sampled from the set  $R_q^{(\ell)}$ .

# 2.2 MLWE-based Public-key Encryption

A generic MLWE-based public-key encryption (PKE) is shown in Fig. 2. It consists of three algorithms: (i) key-generation (PKE.KeyGen) generates public-key pk and secret-key sk, (ii) encryption (PKE.Enc) takes the public-key pk and message m as inputs and generates ciphertext c, and (iii) decryption (PKE.Dec) takes inputs as ciphertext c and secret-key sk and recovers the encrypted message. This PKE scheme is indistinguishable under chosen plaintext attacks (IND-CPA) based on the assumption of the hardness of the MLWE problem. Here, q is a prime modulus, and p, t are power-of-2 moduli. These algorithms use NTT to perform polynomial multiplication efficiently [LN16]. The Compress:  $R_q \longrightarrow R_p$  function is defined

```

PKE.KeyGen()

PKE.Enc(pk:=(seed<sub>A</sub>, \hat{\boldsymbol{b}}), m \in R_{2B}; r)

1. \operatorname{seed}_{\mathbf{A}}, \operatorname{seed}_{\mathbf{se}} \leftarrow \mathcal{U}(\{0, 1\}^{\operatorname{len}_K} \times \{0, 1\}^{\operatorname{len}_K})

1. \hat{\boldsymbol{A}} \leftarrow \text{PRF}(R_q^{(\ell \times \ell)}; \text{seed}_{\boldsymbol{A}})

2. \hat{\boldsymbol{A}} := \operatorname{PRF}(R_q^{(\ell \times \ell)}; \operatorname{seed}_{\boldsymbol{A}}) \quad \triangleright (\hat{\boldsymbol{A}} = \operatorname{NTT}(\boldsymbol{A}))

2. \hat{\boldsymbol{A}} := \operatorname{PRF}(R_q^{(\ell \times \ell)}; \operatorname{seed}_{\boldsymbol{A}}) \quad \triangleright (\hat{\boldsymbol{A}} = \operatorname{NTT}(\boldsymbol{A}))

3. \boldsymbol{s}, \boldsymbol{e} := \beta_{\eta}(R_q^{(\ell)} \times R_q^{(\ell)}; \operatorname{seed}_{\boldsymbol{se}})

3. \boldsymbol{s}', \boldsymbol{e}' := \beta_{\eta}(R_q^{(\ell)} \times R_q^{(\ell)}; r)

3. s', e' := \beta_{\eta}(R_q^{(\ell)} \times R_q^{(\ell)}; r)

4. \hat{\boldsymbol{s}} := \operatorname{NTT}(\boldsymbol{s}) \in R_q^{(\ell)}, \ \hat{\boldsymbol{e}} := \operatorname{NTT}(\boldsymbol{e}) \in R_q^{(\ell)}

4. e'' := \beta_{\eta}(R_q; r||2\ell)

5. \hat{m{b}}\!:=\!(\hat{m{A}}\!\circ\!\hat{m{s}}\!+\!\hat{m{e}})\!\in\!R_q^{(\ell)}

5. \hat{s'} := \operatorname{NTT}(s') \in R_q^{(\ell)}

6. \hat{m{b'}} := \hat{m{A}}^T \circ \hat{m{s'}}

6. return (pk:=(seed<sub>\boldsymbol{A}</sub>, \hat{\boldsymbol{b}}), sk:=(\hat{\boldsymbol{s}}))

7. \boldsymbol{b'} := (\text{INTT}(\boldsymbol{\hat{b'}}) + \boldsymbol{e'}) \in R_q^{(\ell)}

PKE.Dec(sk:=\hat{\boldsymbol{s}}, c:=(\boldsymbol{u}, v))

8. \hat{c_m} := \hat{\boldsymbol{b}}^T \circ \hat{\boldsymbol{s'}}

9. c_m := \text{INTT}(\hat{c_m}) + e'' + \text{Encode}(m) \in R_q

1. \boldsymbol{u'} := \mathtt{Decompress}(\boldsymbol{u},\, p) \in R_a^{(\ell)}

10. \boldsymbol{u} := \mathtt{Compress}(\boldsymbol{b'}, p) \in R_p^{(\ell)}

2. v' := \text{Decompress}(v, t+2^B) \in R_q

11. v := \texttt{Compress}(c_m, t+2^B) \in R_{t+2^B}

з. \hat{\boldsymbol{u'}} := \operatorname{NTT}(\boldsymbol{u'}) \in R_q^{(\ell)}

12. return c := (\boldsymbol{u}, v)

4. \hat{u''} := \hat{u'}^T \circ \hat{s} \in R_q

5. m'' := v' - \text{INTT}(\hat{u''}) \in R_q

6. m' := \mathtt{Decode}(m'') \in R_{2^B}

7. return m'

```

Figure 2: MLWE based IND-CPA secure PKE using NTT

as  $\mathsf{Compress}(x') = \frac{px' + \lfloor q/2 \rfloor}{q} \mod p$ .  $\mathsf{Decompress}: R_p \longrightarrow R_q$  is defined as  $\mathsf{Decompress}(x) = \lfloor \frac{q}{p} \rceil x$ . The  $\mathsf{Encode}: R_{2^B} \longrightarrow R_q$  is defined as  $\mathsf{Encode}(m) = \lfloor \frac{q}{2^B} \rceil m$  and the  $\mathsf{Decode}: R_q \longrightarrow R_{2^B}$  is defined as  $\mathsf{Decode}(m'') = \frac{2^B m'' + \lfloor q/2 \rfloor}{q} \mod 2^B$ . Compress, Decompress, Encode, and Decode operations are applied coefficient-wise to each polynomial and vector of polynomials.

# 2.3 MLWE-based Key Encapsulation Mechanism

The PKE scheme described in Sec. 2.2 is IND-CPA. Indistinguishability under adaptive chosen ciphertext attack (IND-CCA) is a stronger security notion than IND-CPA and is desired to construct a KEM. The IND-CPA PKE in Fig. 2 is converted to IND-CCA KEM by applying a variant of Fujisaki–Okamoto (FO) transformation [HHK17]. As the PKE scheme is based on the MLWE problem, the PKE scheme is not perfectly correct (when the decryption of the encrypted message does not return the original message). If the underlying PKE is  $(1-\delta)$ -correct, then the KEM based on the PKE is also  $(1-\delta)$ -correct [HHK17]. Jiang et al. [JZC<sup>+</sup>18] proposed a IND-CCA KEM construction from a IND-CPA  $(1-\delta)$ -correct PKE in the quantum random oracle model, and a slightly modified version of it is used in FrodoKEM [BCD<sup>+</sup>16]. The KEM shown in Fig. 3 closely follows the FrodoKEM construction. The IND-CCA MLWE-

```

KEM.KeyGen()

\texttt{KEM.Encaps}(\overline{\mathbf{pk}} := (\mathbf{seed}_{\boldsymbol{A}}, \hat{\boldsymbol{b}}))

1. (pk := (seed_{\boldsymbol{A}}, \hat{\boldsymbol{b}}) sk := (\hat{\boldsymbol{s}})) := PKE.KeyGen()

1. msg \leftarrow \mathcal{U}(\{0, 1\}^{len_K})

2. pkh := \mathcal{H}(pk) \in \{0, 1\}^{len_K}

2. m := \texttt{Arrange\_msg}(msg) \in R_{2^B}

3. (K,r) := \mathcal{G}(\mathcal{H}(\overline{\mathrm{pk}}),m) \in \{0,1\}^{\mathrm{len}_K} \times \{0,1\}^{\mathrm{len}_K}

3. z \leftarrow \mathcal{U}(\{0, 1\}^{\text{len}_K})

4. c := PKE.Enc(\overline{pk}, m; r)

(\overline{pk} := pk = (\text{seed}_{\boldsymbol{A}}, \hat{\boldsymbol{b}}), \overline{sk} := (\hat{\boldsymbol{s}}, z, pkh, \overline{pk}))

5. return (c, K)

KEM.Decaps(\overline{sk} := (\hat{s}, z, pkh, \overline{pk}), c)

1. m' := PKE.Dec(\hat{s}, c)

2. msg' := 0riginal_msg(m') \in \{0, 1\}^{len_K}

3. (K', r') := \mathcal{G}(pkh, m') \in \{0, 1\}^{len_K} \times \{0, 1\}^{len_K}

4. m'' := Arrange_msg(msg') \in R_{2B}

5. c_* := \texttt{PKE.Enc}(\overline{\text{pk}}, m''; r')

6. K'' := \mathcal{H}(c, z)

7. if c = c_* then return K := K'

8. else return K := K''

```

Figure 3: MLWE based IND-CCA secure KEM using NTT

based KEM consists of three algorithms: (i) key-generation (KEM.KeyGen), (ii) encapsulation (KEM.Encaps), and (iii) decapsulation (KEM.Decaps). These algorithms use two hash functions, namely  $\mathcal{G}:\{0,1\}^*\longrightarrow\{0,1\}^{2*\operatorname{len}_K}$  and  $\mathcal{H}:\{0,1\}^*\longrightarrow\{0,1\}^{\operatorname{len}_K}$ . We also used two other functions. Arrange\_msg: $\{0,1\}^{\operatorname{len}_K}\longrightarrow R_{2^B}$  is defined by Arrange\_msg(msg) = m, where each of the coefficients of m consists of B bits of msg. If  $n>\operatorname{len}_K$  and  $\frac{n}{\operatorname{len}_K}=\operatorname{repeat}>1$ , then repeat coefficients of m consist of the same bit of msg. Original\_msg: $R_{2^B}\longrightarrow\{0,1\}^{\operatorname{len}_K}$  is the inverse function of Arrange\_msg. Therefore, Original\_msg(Arrange\_msg(msg)) = msg. These two functions work as a repetition code with a majority vote when  $\frac{n}{\operatorname{len}_K}>1$  and random coin flip in case of ties. We discuss these in more detail in Sec. 3.1.

### 2.4 Related works

Most of the current lightweight PKC schemes are based on ECC [HB10, BMS<sup>+</sup>06, HWF08, BGK<sup>+</sup>06] which are not secure against quantum adversaries. Lattice-based constructions are promising candidates for designing lightweight PQC schemes. The NIST standard lattice-based KEM (e.g. Kyber [BDK<sup>+</sup>18]) or the finalists of NIST standardization (e.g. Saber [DKRV18]) are mainly designed keeping security and performance in mind. Afterward, LW implementations of these schemes have been proposed. For reference, Huang et al. [HHLW20], Xing and Li [XL21], Ni et al. [NKLO23] proposed optimized implementations of Kyber in various hardware platforms. Roy and Basso [RB20] presented an implementation of Saber on FPGA hardware, and Ghosh et al. [GBK<sup>+</sup>22, GBK<sup>+</sup>23] proposed an area and energy-optimized implementation of Saber in ASIC. There are several hardware or hardware/software co-designs of Kyber available [BSNK19, DFA<sup>+</sup>20, BUC19].

An RLWE-based encryption scheme with binary secrets and errors, called Ring-BinLWE, was proposed in  $[BGG^+16]$  suitable for lightweight PKC applications. Subsequently, more efficient variants of this scheme have been published in the following works  $[LAM^+22, XHW21, EBSMB19, HGX21]$ . However, these schemes are only IND-CPA secure and hence vulnerable to the chosen ciphertext attacks (CCA). Later on, Ebrahimi et al. [EBS20] proposed a CCA secure version of the IND-CPA Ring-BinLWE scheme, but the quantum bit security provided by this scheme is <75. This is relatively lower in comparison to Saber and Kyber, which provide at least 100-bit core-SVP PQ security even in their lowest security versions. There is always a trade-off between efficient implementation in the resource-constrained platform and security, and not much work has been devoted towards designing lightweight PQC without compromising security.

During the NIST PQC standardization procedure, a suite consisting of three learning with rounding (a variant of LWE problem) based PQC KEMs, Scabbard, was proposed in [BKKV21]. This work explored new design choices, such as a small polynomial size with  $n\!=\!64$  for one of the schemes (Espada) to reduce the memory footprint of the implementation on the resource constraint Cortex-M4 device. Before that, the smallest polynomial size n used in (R/M)LWE-based KEM was 256. In addition to this, several new designs of LWE-based KEMs, such as Smaug [CCHY23], TiGER [PJP+22], etc., have been submitted in the ongoing Korean PQC competition [Kpq]. Although the aforementioned works improved the state-of-the-art of LBC with different design choices and implementations, none of them explored all the possible design choices of LWE-based KEMs from the perspective of lightweight hardware implementations.

# 3 Rudraksh: Design Space Exploration

Designing a cryptographic scheme is fundamentally solving a multidimensional optimization problem where the primary objective functions are attaining a particular level of security, reducing latency and bandwidth (the size of the public key, ciphertext, and secret key). However, we impose new constraints on our lightweight design, such as low memory, low energy, and low area requirements to execute the scheme with reasonable latency. Our LBC design is influenced primarily by 3 parameters, the structure of the module *i.e* the rank of

the matrix  $\ell$  and the size of the constituent polynomials n, the prime modulus q, and the standard deviation  $\sigma$  of the secret or error distribution. In this section, we discuss our design decisions and the rationale behind them in choosing these variables to achieve our design objective of a lightweight KEM.

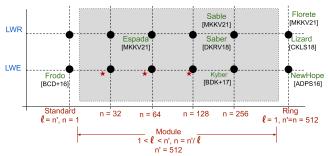

# 3.1 Module space exploration

Keeping the q and  $\sigma$  fixed, the security of the standard, module, or ideal lattice-based cryptographic scheme is dependent on the dimension n' of the underlying lattice only. Module lattices present a convenient and generic representation of different lattices; therefore, in this section, we will use the modules to describe different types of lattices. Let us consider a square module lattice  $A \in R_q^{(\ell \times \ell)}$ . The rank of the underlying lattice is  $n' = \ell \times n$ . Upon fixing n=1 and  $\ell=n'$ , we get a standard lattice. On the other hand, if we fix  $\ell=1$  and n'=n i.e. our lattice consists of a single polynomial, and we get an ideal lattice (RLWE). Indeed, for a long time before the proposal of module lattices [LS15], these two extremities were the only two choices available to design lattice-based cryptosystems, as shown in Fig. 4. Although Kyber [BDK<sup>+</sup>18], Saber [DKRV18], and Dilithium [DKL<sup>+</sup>18] are prominent examples of cryptographic schemes based on module lattices, a vast spectrum of lattice configurations with different values of  $\ell$  or n have been left unexplored. This is shown in Fig. 4 as a grey-shaded region. We explore this region to find optimal choices for n and  $\ell$ to design a lightweight KEM. It should be noted that this is not trivial. Intuitively, one might think that choosing a small n would immediately lead to a lightweight design as it reduces the size of the multiplier. However, to maintain the n' for the security, decreasing nincreases  $\ell$ . This implies more multiplications, more random numbers, larger moduli, etc. Similarly, just decreasing  $\ell$  is also not useful for LW designs. We have to strike a delicate balance between  $\ell$  and n and other metrics that influence the scheme's suitability for small resource-constrained devices. We discuss these different metrics and how they are affected by different values of n and  $\ell$  below.

Memory consumption: The matrix-vector multiplication is performed in PKE.KeyGen (therefore in KEM.KeyGen) and PKE.Enc (therefore in KEM.Encaps and KEM.Decaps) algorithm (shown in Fig. 2). The storage requirement for the public-matrix  $\boldsymbol{A}$  is one of the most memory-expensive operations for the LWE or LWR schemes that use module lattice structure. It requires storing  $\ell \times \ell$  polynomials of degree n-1. Currently, the de-facto standard of lattice-based implementation is to generate this matrix using the just-in-time [KBRV18] strategy. This method generates the matrix  $\boldsymbol{A}$  one polynomial at a time by utilizing the sponge-based periodic '..squeeze-absorb-squeeze.' operation of the extended output function (XOF) such as Keccak [BDPV13]. Therefore, the memory requirement to perform the matrix-vector multiplication is proportional to the size of one single polynomial. As we move towards the left of Fig. 4, polynomial size n decreases. So, although  $\ell$  has to be increased to maintain the security level, the memory requirement in this configuration is smaller. We store a single polynomial for all the polynomial multiplications in hardware platforms. Of course, one can take extreme measures such as generating a single coefficient at a time and performing a single integer multiplication to reduce memory. However, it would drastically deteriorate performance.

In the MLWR-based schemes, the error vectors are generated implicitly. This implies that we do not need to invoke the XOF (or the CBD) module to generate the error vectors in the MLWR-based schemes. Nevertheless, we need to invoke these modules to generate secret vectors in both MLWR and MLWE-based schemes. Therefore, we need these modules on the hardware in either of these schemes. Hence, the implicit generation of error vectors in MLWR-based schemes offers no advantage from area-optimization point-of-view. Also, for the rounding operation, in MLWR-based schemes such as Saber [DKRV18], the modulus

$<sup>^1</sup>$ **A** in (M/R)LWE-based KEMs (or (M/R)LWR-based KEMs) is a square-matrix (i.e., number of rows = number of columns) to ensure the same security of key-generation (which uses **A**) and encapsulation (which uses **A**<sup>T</sup>) as described in [LP11].

and the rounding modulus are chosen as power-of-two numbers. Due to this, MLWRbased KEMs use Toom-Cook-based polynomial multiplication, which generally consumes a relatively larger area/power/latency than NTT-based multiplication used in MLWE-based schemes [KNK<sup>+</sup>24]. In MLWE-based KEMs that support NTT natively,  $\hat{\mathbf{A}} \in R_a^{(\ell \times \ell)}$  can be sampled directly from the NTT domain instead of first sampling  $\boldsymbol{A}$  and then performing NTT(A) to generate  $\hat{A}$ . However, one can also perform the evaluation stage of Toom-Cook multiplication (evaluation-schoolbook multiplication-interpolation) and store it [BKV20, KRS19]. However, it is not in-place like NTT and requires more memory than the original A. Although following the work of Chung et al. [CHK<sup>+</sup>21], an NTT can be used for MLWR-based schemes by choosing a large NTT-friendly prime that envelopes the modulus and growth of error during multiplications. This strategy helps MLWR-based schemes, such as Saber, achieve performance comparable to Kyber on the ARM Cortex-M4 platform. However, the area requirement (or the stack memory of Cortex-M4 implementations [ACC+21]) increases significantly for MLWR-based KEMs due to their larger modulus. Recently, three MLWR-based KEMs have been proposed in [BKKV21] and their hardware implementation in [KNK<sup>+</sup>24]. This work shows that Toom-Cook-based polynomial multiplication can be made resource-constrained at the cost of more cycles. Therefore, we explore possible MLWE schemes with smaller polynomial sizes, which can be implemented with low resources without much performance degradation. We primarily target schemes where n is power-of-2 and less than 256, such that 128, 64, and 32.

Multiplier size: In the case of a standard lattice-based scheme with matrix rank n', one of the most computation-heavy operations is multiplications between  $n' \times n'$  matrix and n' length vector. For the ring lattice-based scheme, we have to perform polynomial multiplications between two n'-1 degree polynomials to achieve a similar level of security. This can be done using quasi-linear NTT multiplication. Hence, for a particular security level, the ring lattice-based schemes are more efficient than the standard lattice-based schemes in terms of computational cost. However, the resource consumption in that case is relatively huge as two n'-1 degree polynomials must be stored to perform the polynomial multiplication. Therefore, for a specific security level, due to the just-in-time strategy, the module lattice-based schemes are more beneficial in reducing resource consumption than the ring lattice-based schemes. Although we have to perform multiple polynomial multiplications due to the use of module structure, module lattice-based schemes perform better than the standard lattice-based schemes. The choice of the hard problem i.e. MLWE or MLWR, and polynomial size determines the size of the multiplier in hardware. Nevertheless, the resource consumption is proportional to the size of a single polynomial for module lattice-based schemes. Therefore, choosing the hard problem and polynomial size is one of the leading factors when designing an efficient scheme for resource-constrained devices. Generally, the size of the polynomial n is chosen in multiple with the size of the secret message (msg) bit-length len<sub>K</sub> [ADPS16, BDK<sup>+</sup>18, CKLS18]. If  $n > \text{len}_K$ , B = 1, and  $\frac{n \cdot B}{\text{len}_K} = \text{repeat}$  for an integer repeat > 1, we use repeat coefficients of ciphertext polynomial v (generated during the encryption algorithm shown in Fig. 2) to hide a single message bit of msg by replicating a single message-bit repeat times using Arrange\_msg function. Please note that we use repeat > 1 of the message bits only when  $n > len_K$ , otherwise repeat = 1. We now discuss the process of calculating failure probability when the repeat is greater than 1. For example, if repeat=3, the failure happens when at least two of the three message bits are decoded to the wrong value. Then the new failure probability is calculated as  $(3 \cdot (fail\_prob)^2 \cdot (1 - gaussian + g$ fail\_prob))+(fail\_prob)<sup>3</sup>, where fail\_prob is the failure probability when repeat=1 (no repetition). If repeat=4, the failure occurs when at least three of the four message bits are decoded to the wrong value. Failure also occurs when two of the four message bits are wrong with half probability (as in this case, one of the two choices would be chosen randomly, which can be correct with only half probability). Then the new failure probability is calculated as  $(3 \cdot$  $(\text{fail prob})^2 \cdot (1 - \text{fail prob})^2) + (4 \cdot (\text{fail prob})^3 \cdot (1 - \text{fail prob})) + (\text{fail prob})^4$

This calculation changes depending on repeat. However, we would like to mention that a designer can choose various approaches to encode message bits into the ciphertext polynomial when  $n > \text{len}_K$ . Unlike the error correcting code used in LAC [LLZ<sup>+</sup>18] where timing attack has been shown in [DGJ<sup>+</sup>19], the Arrange\_msg (and also Original\_msg) function can be implemented in a constant-time manner. Now, if the polynomial-size n is smaller than the size of the message bit-length  $\text{len}_K$  i.e.  $n = (1/B) \cdot \text{len}_K$  for an integer B > 1. In that case, we have to encode B message bits into a single coefficient of ciphertext polynomial v [BCD<sup>+</sup>16] as displayed in Fig. 2. This would increase the requirement of the reconciliation bits  $(\log_2 t)$  and eventually the modulus of a coefficient of v (= $\log_2 t + B$ ). This will require a larger modulus q, which reduces the security. We will discuss this phenomenon in more detail in Sec. 3.2.

Figure 4: Design space of lattice-based KEMs depending on the different variations of LWE problems and underlying ring sizes. Our explored module spaces are marked with red stars.

Flexible design: Module lattices present an opportunity to design cryptographic schemes that benefit the IoT architecture as discussed in Sec. 1. The structure of module lattices can be utilized to instantiate such a flexible scheme. Let us assume a cryptographic scheme uses a module lattice of size  $\ell \times \ell$ . An extremely low latency and high resource-consuming implementation can be realized by implementing  $\ell^2$  multipliers in parallel, and an extremely lightweight and high latency version can be realized by implementing a single multiplier repeatedly using for  $\ell^2$  times. Here, of course, the XOF has to be implemented accordingly to match the latency of the multiplier. As discussed before, polynomial arithmetic, specifically polynomial multiplication, is one of the major bottlenecks in LBC's performance and resource consumption. The polynomial size in both Kyber and Dilithium is 256. Even in the most lightweight instantiation, an IoT peripheral device has to use a 256×256 polynomial multiplier (more specifically, NTT multiplication, which includes size-256 NTT, size-256 INTT and size-256 point-wise multiplication). This is still very expensive for an IoT peripheral device. A smaller polynomial size is more suitable with some sacrifice in efficiency. Therefore, a balance has to be struck between these two metrics for a suitable lattice-based PQ scheme for IoT.

In conclusion, ring lattice-based schemes are especially advantageous for achieving better performance, but they require more hardware area. Meanwhile, standard lattice-based schemes theoretically can be implemented with lesser memory and area at the expense of substantial computation costs. Module lattice-based schemes with polynomial-size n and underlying lattice's matrix rank  $n'=\ell\times n$  provide a trade-off between them. If we keep n' constant, and increase  $\ell$  then n decreases proportionately, which reduces the memory requirements for a single polynomial. However, this increases the generation cost of the matrix  $\boldsymbol{A}$ , as the matrix consists of  $\ell\times\ell\times n\times\lceil\log_2q\rceil$  pseudo-random bits. These pseudo-random numbers are generated by using an XOF, which is another computationally expensive operation as described later in Sec. 3.5. If memory is not a concern, then increments of  $\ell$  can be used to increase parallelism in hardware implementations. There are some module LWR-based designs that have been proposed in recent years [DKRV18, BKKV21]. However, the module-space for designing different MLWE-based schemes remained mostly unexplored. Therefore, we choose to explore the module space for the LWE problem denoted by red colored stars in Fig. 4 to construct a lightweight MLWE-based KEM with optimal parameters.

#### 3.2 Choice of moduli

It is clear from the discussion in the previous section that we want to explore the module lattice space to design LW lattice-based KEM. LWE-based schemes use reconciliation mechanisms by sending some extra bits [BDK<sup>+</sup>18] (t in Fig. 2). These bits help to recover the encrypted message during the decryption algorithm by reducing the noise introduced during the encryption procedure called decryption noise (as LWE-based encryption schemes are not perfect). Increased decryption noise induces an increment in the failure probability, which can cause a decryption failure attack [DGJ<sup>+</sup>19]. As discussed earlier, a smaller polynomial size n reduces the memory consumed by a single polynomial and also the area required to implement single polynomial multiplication in hardware. But, if we reduce the size of the polynomial n, then we have to encode multiple message bits in a coefficient of v. This will increase the failure probability. This can be compensated by more reconciliation bits i.e., larger t, which in turn increases q and the ciphertext size.

The security of a lattice-based cryptosystem increases with the increase in the error-to-modulus ratio, i.e. keeping the error distribution fixed, the security will reduce with the increase in the value of q, and vice versa. Therefore, a smaller value of q helps to increase efficiency, reduce computational and storage resources, and also reduce the bandwidth (size of the public-key, secret-key, and ciphertext), but increases the failure probability. Hence, we concentrated on finding an optimal value of the modulus q for which the decryption failure would be minimal. We also proposed implementations with minimal hardware resources. The type of the modulus i.e prime vs. power-of-2 modulus also has a significant impact on the performance and resource utilization of the scheme. We have deferred this discussion till Sec. 3.3.

### 3.3 Choice of polynomial multiplication

For LBC schemes, polynomial multiplication is one of the major bottlenecks with respect to efficiency and resource consumption. In literature, there exist mainly two types of polynomial multiplication algorithms for implementing LBC schemes: i) Toom-Cook multiplication [Too63, Coo66], and (ii) NTT multiplication [Pol71, LN16]. Toom-Cook multiplication is relatively simpler and can be used for any modulus. However, the time complexity of the Toom-Cook polynomial multiplication is asymptotically slower  $O(n^{1+\epsilon})$ , where  $0 < \epsilon < 1$ . On the other hand, NTT multiplication is the most used polynomial multiplication for implementing LBC schemes due to its faster quasi-linear time complexity  $(O(n\log_2 n))$ . However, for the NTT multiplication, the modulus q needs to be NTT friendly i.e. a prime number with the primitive 2n-th root-of-unity in the prime field  $\mathbb{Z}_q$ . Please note that, for small values of n, the efficiency of Toom-Cook polynomial multiplication with a power-of-2 modulus (as modular reduction is free in a power-of-2 ring) and NTT-based polynomial multiplication on an appropriate prime modulus is comparable when performed the full multiplication. However, for LBC schemes, we can sample the public matrix  $\mathtt{NTT}(A) = \hat{A}$  from  $R_q^{(l \times l)}$  using  $seed_A$  instead of sampling  $\boldsymbol{A}$  and performing NTT on  $\boldsymbol{A}$ . It can save cycles while computing  $\boldsymbol{A} \cdot \boldsymbol{s}$  as  $\boldsymbol{A}$  is random implies NTT(A) is random and vice-versa. We also can save execution time on the NTT-based polynomial multiplication by omitting the INTT operation and keeping the multiplication result in the NTT domain (e.g., Line (5) in the PKE.KeyGen() in Fig. 2). This makes the LBC scheme with NTT multiplication more efficient than Toom-Cook multiplication. Therefore, we choose to use NTT-based polynomial multiplication over a prime modulus q.

NTT multiplication between two polynomials a and b from  $R_q$  is performed by  $a \cdot b =$ INTT(NTT $(a) \circ$ NTT(b)). Given  $\zeta$  is the 2n-th primitive root of unity and  $\omega = \zeta^2$ , the NTT $(x) = \hat{x} =$

$(\hat{x}_0, \hat{x}_1, ..., \hat{x}_{n-1})$  and  $INTT(\hat{x}) = x = (x_0, x_1, ..., x_{n-1})$  are denoted by the following Eq. 1 & 2.

$$\hat{x_i} = \sum_{j=1}^{n-1} x_j \zeta^{(2i+1)j} = \sum_{j=1}^{n-1} (x_j \zeta^j) \omega^{ij} \mod q, \, 0 \le i \le n-1.$$

(1)

$$x_j = 1/n \sum_{i=1}^{n-1} \hat{x}_i \zeta^{-(2i+1)j} = \zeta^j / n \sum_{i=1}^{n-1} \hat{x}_i \omega^{-ij} \mod q, \, 0 \le j \le n-1.$$

(2)

In this procedure of multiplication, we have to store the pre-computed values of  $\zeta^j$  mod q (for  $1 \le j \le n-1$ ) along with the coefficients of two participated polynomials for improving the performance. Therefore, the total memory requirement to perform multiplication depends on polynomial size n.

In the literature, there is another type of NTT called incomplete NTT multiplication, where the NTT multiplication between two n size polynomials is replaced by two separate NTT multiplications between two n/2 size polynomials. Karatsuba multiplication is performed on the last 1-degree polynomials. Therefore, incomplete NTT multiplication requires more modular multiplications than complete NTT multiplication. Yet, the incomplete NTT multiplications outperform complete NTT multiplications [AABCG20] on software by omitting several reduction steps after modular multiplication. Incomplete NTT multiplication is also used in Kyber. We employ a single butterfly module shown in Fig. 8 that includes a reduction step for performing NTT, INTT, and PWM in our KEM. Therefore, incomplete NTT multiplication increases the latency in our KEM implementation. Consequently, we choose the complete NTT multiplication over the incomplete one for polynomial multiplication. More details regarding NTT multiplication are provided in Sec 4.2.

#### 3.4 Secret and error distribution

In LWE-based schemes, coefficients of secret and error are usually sampled from a narrow distribution. There are several (M/R)LWE-based KEMs that have utilized discrete Gaussian distribution as secret and error distribution [BCD<sup>+</sup>16]. Unfortunately, it is hard to implement a Gaussian sampler efficiently and securely against timing attacks. For KEMs, Alkim et al. [ADPS16] showed that this Gaussian distribution can be replaced with a centered binomial distribution (CBD) whose standard deviation is the same as the Gaussian distribution. The sampling from a CBD is much simpler and easier to protect against side-channel attacks. Several other distributions have been explored in the design of LWE-based schemes to gain efficiency, such as binary distribution [BGG<sup>+</sup>16], fixed weight distribution [BBF<sup>+</sup>19, CCHY23, PJP<sup>+</sup>22], etc. However, as our goal was to design a Kyber-esque scheme, we had limited our search space to CBDs ( $\beta_{\mu}$ ) with different  $\mu$ . The above-mentioned other distributions can also be potentially used as secret and error distributions for lightweight cryptography, but we have not investigated them in this work.

The parameter  $\mu$  impacts the security parameters of a CCA secure scheme, failure probability, and bit security. The standard deviation of  $\beta_{\mu}$  is  $\sqrt{\frac{\mu}{2}}$ . Suppose the modulus q and the rank of the lattice n' are fixed. In that case, both the bit security and the failure probability of the scheme increase as the standard deviation (for CBD,  $\mu$ ) increases. The sampling from a CBD  $\beta_{\mu}$  is accomplished by performing  $\mathrm{HW}(a) - \mathrm{HW}(b)$ , where a, b are  $\mu$  bit pseudo-random numbers. The parameter  $\mu$  of CBD is crucial in deciding the scheme's efficiency. The CBD sampler uses pseudo-random numbers, and the bigger the CBD parameter  $\mu$ , the more pseudo-random numbers generation will be required. Pseudo-random numbers are generated using some extendable-output function (XOF). The XOF is one of the costliest operations in terms of computation and resources (Details about XOF have been provided in the next subsection). Finding a smaller  $\mu$  is necessary for better performance, less resource utilization, and lower failure probability. However, a larger  $\mu$  increases the

bit security. As we are aiming for a CCA-secure KEM scheme with 100-bit Core-SVP PQ security using FO transform [HHK17], the failure probability must be  $\leq 2^{-100}$ .

Hence, in our design, we have analyzed these aspects with a wide range of values of  $\mu$  to find an optimal choice to strike a balance between the security and efficiency of our scheme.

### 3.5 ASCON based hash and XOF functions

The implementations of LBC exhibit a unique and interesting phenomenon. Lattice-based cryptographic schemes use a lot of pseudorandom numbers to generate the matrix  $\hat{A}$  and the secret s and error e vectors. From a designer's perspective, generating pseudorandom numbers is considered an auxiliary function that does not impose major overhead on executing the whole scheme. More focus is given to optimizing the core functions of the cryptographic scheme as they consume the majority of the time and resources in various implementations. This is true for classical PKC (and symmetric-key ciphers also) schemes such as RSA [RSA78] and ECC [Mil85], where most of the time and resources are spent on making the multiprecision multiplications and scalar point multiplication, respectively. However, for LBC, the standard approach of generating pseudorandom numbers is using an XOF such as Keccak [BDPV13]. This process takes close to or, in some cases, more than 50% of total time and/or area [XL21]. As numerous works have been done to optimize the core operation of LBC, which is polynomial multiplication in software and hardware platforms [RB20, BTK+20], the process of random number generation has become the bottleneck.

To alleviate this problem, designers have proposed alternative versions of their schemes, such as Kyber-90s [ABD+21] or Saber-90s [BBD+21] where they proposed to generate the random numbers using a block cipher (such as AES [Can05]) in counter mode. While this could be a good solution for software and hardware platforms with dedicated support for these block ciphers, such as the AES-NI instruction set, for standalone hardware with minimal software support, this is not a good solution. As shown in Fig. 3 (for  $\mathcal{G}$ ,  $\mathcal{H}$ ), we need to use secure hash functions for a CCA-secure KEM using the FO transformation. Therefore, we cannot completely remove the Keccak module from the hardware platform. Moreover, we must include another module implementing the block cipher algorithm. Another strategy for reducing the overhead of Keccak could be using round-reduced Keccak [BDH+23] to generate  $\hat{A}$ ,  $\hat{s}$ , and  $\hat{e}$  ( $\hat{s}'$ ,  $\hat{e}'$ ,  $\hat{e}''$ , where only uniform randomness is needed [pqc24]. However, there is not enough research to engender enough confidence to use the round-reduced Keccak as a reliable pseudo-random number generator. Therefore, more research is required to determine the security versus efficiency trade-off. Moreover, we wanted to use a standard hash/XOF function, which went through several security analyses in our scheme.

Therefore, the best possible solution in this scenario is to replace the bulky Keccak module with some lightweight alternative. NIST concluded its lightweight cryptography competition [NIS23a] in February 2023 and selected the ASCON [DEMS12] family of lightweight ciphers. Like Keccak, ASCON is also based on the sponge construction [BDPV11] and can be used as a Hash function and XOF. Moreover, ASCON is specifically designed for lightweight implementation on resource-constrained devices. This makes ASCON an ideal choice for replacing the Keccak function in our design. However, this is not very straightforward. The biggest hurdle is the difference in the state size of these two ciphers, which are 320 and 1600 bits for ASCON and Keccak, respectively. Therefore, each ASCON-squeeze outputs a fraction of pseudorandom bits compared to a Keccak-squeeze. Hence, to utilize ASCON's full potential, we have carefully designed our architecture exploiting the lightweight sub-layer and linear layer of ASCON, as well as meticulous scheduling and memory organization in the FPGA implementation such that the smaller throughput does not become the operational bottleneck (explained in Sec. 4.3). Another hurdle in replacing Keccak with ASCON is that the current version of ASCON provides maximum 128-bit security; therefore, it is unsuitable to replace SHAKE-256 or SHA3-512, which has been used in Kyber for higher security versions. However, it is fine for our lightweight design. Due to these issues, replacing Keccak

Table 1: Parameter set of all the explored designs of KEMs together with Kyber and NewHope for NIST-level-1 security.

| Scheme<br>name   | Module<br>Parameter |     | Primary<br>modulus |                          | Compression<br>modulus   |                          | CBD<br>parameter |          | Encoding | Bit-security         | Failure<br>probability |

|------------------|---------------------|-----|--------------------|--------------------------|--------------------------|--------------------------|------------------|----------|----------|----------------------|------------------------|

|                  | $\ell$              | n   | q                  | $\lceil \log_2 q \rceil$ | $\lceil \log_2 p \rceil$ | $\lceil \log_2 t \rceil$ | $\eta_1$         | $\eta_2$ | B        | (Quantum, Classical) | probability            |

| KEM-poly32       | 21                  | 32  | 31873              | 15                       | 12                       | 3                        | 2                | 2        | 4        | (105, 116)           | -113                   |

| KEM-poly64       | 9                   | 64  | 7681               | 13                       | 10                       | 3                        | 2                | 2        | 2        | (104, 114)           | -128                   |

| KEM-poly128      | 4                   | 128 | 3329               | 12                       | 10                       | 2                        | 2                | 2        | 1        | (101, 111)           | -179                   |

| Kyber [ABD+21]   | 2                   | 256 | 3329               | 12                       | 10                       | 3                        | 3                | 2        | 1        | (107, 118)           | -139                   |

| NewHope [ADPS16] | 1                   | 512 | 12289              | 14                       | 14                       | 2                        | 4                | 4        | 1        | (101, 112)           | -213                   |

with ASCON and achieving efficiency is not straightforward.

### 3.6 Parameters of our scheme

We target to attain at least 100-bit post-quantum core-SVP security for our lightweight KEM. It will provide equivalent security with AES-128 [AAC<sup>+</sup>22] and belong to the NIST-level-1 security category. Therefore, the current version of ASCON with 128 bit security is enough for us. In this section, we discuss the process of finding parameters for Rudraksh.

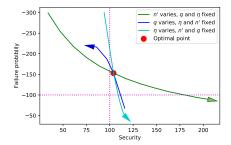

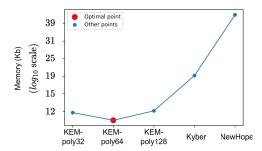

Leaky-LWE estimator [DSDGR20] is the state-of-the-art tool to estimate the hardness of the underlying LWE problem. It uses the best-known lattice reduction algorithm Block Korkine-Zolotarev (BKZ) [SE94, CN11] algorithm. BKZ algorithm primarily estimates the difficulty of solving the shortest vector problem (SVP) in a smaller lattice. This is known as core-SVP hardness. The security of the overall LBC scheme is the hardness of this core-SVP problem with some polynomial overhead. Usually, we ignore this polynomial overhead for a pessimistic estimate of security. The leaky-LWE estimator tool takes the underlying base matrix rank  $n' = \ell \times n$ , the modulus q, and the standard deviation of secret or error distributions of a scheme as input. It returns both post-quantum and classical bit security of the corresponding scheme. As discussed earlier, while designing a module lattice-based scheme for resource-constrained devices, the two most important parameters are the polynomial-size n and the length of the vector  $\ell$ . We have viewed finding the optimal parameter set for our lightweight KEM as a multi-dimensional optimization problem. First, we fixed the polynomial-size n and exhaustively searched all the possible values of other parameters such as the vector length  $\ell$ , modulus q, and CBD parameter  $\eta_1$ ,  $\eta_2$ , etc. This is followed by calculating the resource consumption for these parameters. We have repeated the process for all the power-of-2 polynomial sizes to maintain the efficiency of the scheme as it is beneficial for the implementation of several primary building blocks, such as NTT multiplication, Encode, Decode functions, etc. We also did not explore the polynomial-size below n = 32, as the failure probability increases in these cases drastically. We have to increase the modulus q a lot to counteract the high failure probability, affecting the scheme's efficiency. To attain the targeted security, we have to increase the length of vectors, which will also affect the scheme's efficiency. We provide optimal parameter sets for three configurations (i) KEM-poly32: with polynomial-size 32, (ii) KEM-poly64: with polynomial-size 64, (iii) KEM-poly128: with polynomial-size 128. The parameters of all these configurations are shown in Tab. 1. This table also includes the parameters of Kyber [ABD+21], where the n=256, and NewHope [ADPS16], where n=512=n'. We also provide the process to find parameters for KEM-poly64 in Fig. 5. To calculate the failure probabilities, we followed the exhaustive search strategy similar to other LWE-based schemes, such as Kyber, Saber, NewHope, etc. While exploring the KEMs of this work, i.e., KEM-poly32, KEM-poly64, and KEM-poly128, we keep repeat=1 (as  $n \leq len_K$ ). Memory and area are two primary benchmarks for hardware resource consumption. The memory possesses all the resources used for data usage, which includes all the on-chip memory structures such as Block-RAM (BRAM), distributed RAM, etc. The area contains the configuration logic resources, including look-up tables (LUTs) and logical elements. Now, we discuss the estimated hardware resource usage of all the schemes presented in Tab. 1 in terms of memory and select the one that can be operated with optimal resources. Each polynomial of the secret-key vector s can be generated from  $seed_s$ . These

Figure 5: Relation between n', q, and  $\eta$  ( $\eta_1/\eta_2$ ) when n=64 is fixed (arrows indicate the direction of increase in values). The parameter set of the optimal point is selected for KEM-poly64.

Figure 6: Memory consumption of the KEM depending on the polynomial size

secret polynomials generate the public-key vector  $\hat{\boldsymbol{b}}$  during the key-generation procedure or used in the PKE.Dec (Fig 2, line (3) in PKE.KeyGen) during the decapsulation algorithm. One polynomial length  $(n \times \lceil \log_2 q \rceil)$  bits) memory storage is required for the secret polynomial (for s in PKE.KeyGen, for s' in PKE.Enc), and for the runtime calculation of single polynomial in the public matrix  $\hat{A}$ . For efficient implementation, another polynomial storage is required for the n roots of unity (or twiddle factors). We use one more polynomial space to save the ciphertext v as well as a vector of polynomial space  $(\ell \times n \times \lceil \log_2 q \rceil)$  bits) to store the public vector  $\hat{\boldsymbol{b}}$  in the key-generation algorithm, and that same space is used to store the ciphertext vector **u** during PKE.Enc. We also need 320-bit ASCON state register for KEM-poly32, KEM-poly64, KEM-poly128, and 1600-bit state register of Keccak for Kyber and NewHope. Extra buffer is often used for post-processing for hash (for K in encapsulation and K', K''in decapsulation) and the pseudorandom number z generated during key generation and used in decapsulation algorithm (for the cases of decryption failure). This buffer size is equivalent to the state register. Therefore, we need memory for four polynomials, one vector of polynomials, states of ASCON or Keccak, and storage for hash output and z. We calculate the storage requirement for each of the configurations of Tab. 1 and present them with the help of Fig. 6. It is evident from Fig. 6 that KEM-poly64 uses the least storage compared to other configurations. Therefore, we select KEM-poly64 as our lightweight KEM Rudraksh and present a lightweight (low-resource) hardware implementation. The public-key, secret-key, and ciphertext sizes of Rudraksh are 952, 1920, and 760 bytes, respectively. These sizes are equivalent to/slightly higher than those of Kyber, which are 800, 1632, and 768 bytes. This is mainly due to our design decisions and prioritizing resource requirements over communication bandwidth requirements. Usually, lightweight devices use protocols such as BLE and ZigBee for data transmission, which are extremely power- and energy-efficient. Regarding the energy consumption for data transmission, our scheme is similar to that of Kyber. Moreover, our design uses a smaller polynomial size, and the encapsulation/decapsulation module of Rudraksh can start its computation after receiving a public-key/ciphertext polynomial. Hence, we can transfer the key/ciphertext one polynomial at a time without affecting the scheme's efficiency. Although this process does not reduce the total number of byte transfers via a network, because of this interleaved operation between communication and computation, our scheme can operate with a smaller bandwidth. Such techniques need to be explored further in the real-world environment.

# 4 Hardware design

After exploring the theoretical design decisions for developing a lightweight lattice-based KEM, we efficiently implement the scheme and show the scheme's area and latency requirements in hardware. We have chosen Xilinx Virtex-7 and Artix-7 FPGAs as our target

Figure 8: Butterfly module's architecture

devices. Our hardware design consists of several components. First, we discuss the system architecture; second, we discuss the re-configurable butterfly architecture; and finally, we discuss the datapath of the ASCON-based XOF function. We also discuss the other computational units, such as the CBD sampler, rejection sampling unit, etc. We also discuss our efficient memory organization, as careful memory organization is crucial for memory reduction. Note that reducing memory is important for lightweight design as most use cases are memory-constrained IoT devices. They will often share the memory with other systems, and careful memory-reduced design is of utmost importance. Efficient NTT memory access removes the need to reorganize memory, which increases latency overhead. Finally, we describe the scheduling during all the operations.

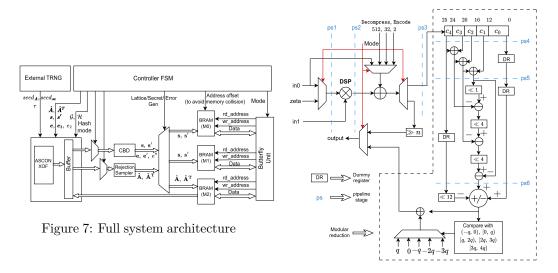

### 4.1 System architecture

The full system architecture is shown in Fig. 7. The seeds of matrix  $\hat{A}$ , secret s, and error e are taken from an external True Random Number Generator for demonstration. A controller FSM controls ASCON-XOF and butterfly units synchronously. It enables/gates the CBD/rejection sampler when not required. For example, sampling  $\hat{A}$  does not require CBD and hence is gated by the controller. The controller also provides an address offset to avoid memory collision with the public/secret key if we want to store them. The ASCON permutation is used for the  $\mathcal{H}, \mathcal{G},$ and PRF functions. It is the key function to generate the public matrix of polynomials  $\hat{A}$ . Each coefficient of the polynomials is  $\lceil \log_2 q \rceil$  bits and less than the prime modulus q. Therefore, an additional rejection sampler is needed to discard coefficients  $\geq q$ , while generating  $\boldsymbol{A}$ . The AS-CON core is also used to generate the pseudo-random number for the CBD sampler module to construct the secret s (or s'). The secret is directly stored in 2 NTT memories. The reconfigurable butterfly unit performs the NTT/INTT/point-wise multiplication(PWM) operation. Synchronous memory access for NTT and INTT are ensured in the design. We discuss the details in Sec. 4.4. PWM is a vector multiplication. Since the polynomial-size is small (64), we use complete NTT multiplication, unlike Kyber, where PWM is complex, as it uses incomplete NTT multiplication along with Karatsuba multiplication in the last step as part of PWM.

### 4.2 Reconfigurable butterfly unit

We introduce a reconfigurable butterfly unit for NTT, INTT, PWM, compress, decompress, encode, and decode functions. The butterfly unit is configured by the 3-bit mode signal provided by the controller (Fig. 8). A single DSP unit is used for multiplication. Notably,

multiplication is a key operation in all the previous computations and takes a significant area. The DSP unit performs the multiplication between the twiddle factor ( $\zeta^j$  mod q where  $1 \leq j \leq n-1$ ) and  $x_j$  in NTT/INTT operations. We adapted Zhang et al.'s [ZYC<sup>+</sup>20] technique for INTT. Here, the multiplication with (1/n) mod q of Eq. 2 is replaced by the (1/2) mod q in each butterfly operation. This step eliminated complex multiplication by 1-bit left shift operation at negligible hardware cost. The butterfly unit also consists of an adder/subtractor, as shown in Fig. 8. Finally, it includes a three-stage pipelined shift-and-add modular reduction, ensuring a very low critical path for the design. It is important to note that ASCON-XOF is extremely lightweight, and its substitution layer consists of a few 'xor' and 'and' gates. Hence, we use 6-stage pipelines in the butterfly to maintain a low critical path, resulting in a high-frequency design.

Only the multiplication and the modular reduction are enabled, while the butterfly operates in PWM mode. We employ the butterfly unit to compute  $\mathsf{compress}(\pmb{b}', 1024)$ , defined by  $(\pmb{b}' \ll 10) + q/2 \over q$  followed by keeping the lower 10 bits (similar to [ABD+20]). The division by q is replaced by multiplication with an approximate value of 1/q. This procedure includes multiplication with  $(2^{32}/q+1)$  followed by 32 bit right shift. We use a similar technique to compute  $\mathsf{compress}(c_m, 32)$ . Here, we substitute the division by q with multiplication with  $(2^{27}/q+1)$  followed by 27 bit right shift. While computing  $\mathsf{Decode}(m)$ , we replace the division by q with multiplication with  $(2^{30}/q+1)$  and followed by 30 bit right shift.  $\mathsf{decompress}(\pmb{u}, 1024) = (q \cdot \pmb{u} + 512) \gg 10$ ,  $\mathsf{decompress}(v, 32) = (q \cdot v + 16) \gg 5$ , and  $\mathsf{encode}(m) = (q \cdot m + 2) \gg 2$  involve a multiplication with q. All the right shift operations are implemented using a configurable barrel shifter. We describe modular reduction hardware in detail below.

Modular reduction: Modular reduction is one of the crucial parts of the butterfly core. Some of the primarily utilized modular reduction algorithms are Montgomery reduction [BDK+18] and Barrett reduction [XL21]. However, it is important to note that while using Montgomery and Barrett reduction following [ABD+21], one extra multiplication followed by the reduction converts a polynomial to the Montgomery domain. Returning from the Montogomery domain often requires one extra multiplication, costing extra latency for an extra DSP unit. Later, for primes like  $q = 2^m \times k + 1$ , where k is an odd number, the k-reduction [LN16] algorithm has been proposed. This reduction algorithm performs better and consumes less area on hardware than the Montgomery or Barrett reduction. Subsequently, the  $k^2$ -reduction algorithm is introduced by Bisheh-Niasar et al. [BAK21], which is more efficient than the k-reduction algorithm. k-reduction algorithm takes input c and outputs  $d \equiv k \times c \mod q$ , and  $k^2$ -reduction algorithm takes input c and outputs  $d \equiv k^2 \times c \mod q$ . We can eliminate the extra  $k^s$ ,  $s \in \{1, 2\}$ , by replacing the pre-computed factor zeta by  $k^{-s} \times \text{zeta}$  during NTT or INTT. However, while using the  $k^s$ -reduction during point-wise multiplication, we have to perform one extra multiplication followed by the reduction to discard the extra  $k^s$  factor. It either increases the number of DSPs (containing one multiplication unit) or the latency. However, this extra step is unnecessary if we use the shift-and-add modular reduction technique. We used this technique for our prime q=7681 and presented it in Alg. 1. It is an improved lightweight hardware-assisted variant of k-reduction. The detailed implementation is shown on the right side of the butterfly unit (Fig. 4.2). The modular reduction only needs addition/subtraction and bit shift operation, making it extremely lightweight and suitable for high-frequency operations.

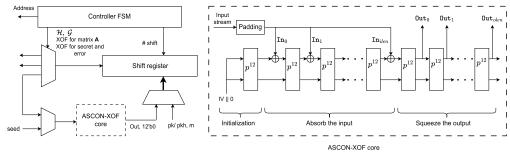

### 4.3 ASCON core as XOF function

ASCON-XOF takes an input of arbitrary size in chunks of 64 bits and generates an output with variable lengths (in chunks of 64 bits). ASCON is also a sponge-based construction like Keccak. It offers a smaller state size of 320 bits (64-bit rate and 256-bit capacity), whereas the Keccak state register size is 1600 bits. ASCON-XOF can be implemented with low-area (Fig. 9). It supports several functional modes which are PRF to generate the public-matrix  $\hat{A}$ , the CBD sampler to generate the secret s (or s'), error e (or e', e''), and  $\mathcal{G}$ ,  $\mathcal{H}$ . The global

```

Algorithm 1: Shift-and-add modular reduction (an improved k-reduction [LN16])

: c \text{ is an integer} \in [0, (q-1)^2]

Input

: d \equiv c \mod q

Output

c = c_4 ||c_3||c_2||c_1||c_0

\triangleright |c_0| = 13, |c_1| = |c_2| = |c_3| = 4, |c_4| = 1

temp_0 = c_4 + c_3; \ temp_1 = temp_0 + c_2; \ temp_2 = temp_1 + c_1

temp_3 = (temp_2 \ll 1) - temp_0; temp_4 = (temp_3 \ll 4) - temp_1

temp_5 = (temp_4 \ll 4) - temp_2; temp_6 = temp_5 + c_0

-c_4 \ll 12) + temp_6

if ((d[15]) == 1) then d += q

if (d>q) then d-=q

if (d > q) then d - = q

if (d>q) then d-=q

return d

```

controller fixes the mode for this block.

ASCON-XOF function has three steps: a) initialization, b) absorb, and c) squeeze. The initial state register is pre-computed from IV in our design to save latency. The second step is to absorb the input stream in the block of 64 bits. In Fig. 9, ilen denotes  $\lceil \frac{\text{input length}+1}{64} \rceil$ . During absorb, 64 bits input block is XORed with the first 64 bits of the state register followed by  $p^{12}$ . The third step is to squeeze the output bits. This process continues until the required length of output is extracted. We denote  $\lceil \frac{\text{output length}}{64} \rceil$  by olen in the figure. ASCON permutation  $p^{12}$  is the primary building block of the ASCON-XOF function. It is used during all the three steps. This permutation consists of three steps: (i) addition of constant round, (ii) substitution layer, and (iii) linear diffusion layer [DEMS12].

The rate of input and output block of ASCON is only 64-bit. ASCON's permutation  $p^{12}$  includes only bit-wise XOR, circular shift, and bit-wise AND operations. Therefore, single permutation takes considerably less number of gates than Keccak. Moreover, this implies that the critical path of the ASCON permutation is small and, hence, increases the maximum frequency. The execution of the ASCON permutation at a higher frequency compensates for high clock cycle consumption during absorb and squeeze functions. It helps this design compute with a similar order of latency as Kyber. This design decision assists in attaining an efficient performance with reduced area usage and makes it especially suitable for lightweight designs.

This ASCON-XOF hardware also contains a 76-bit buffer/shift register. This buffer stores the input of the absorb while computing  $\mathcal{H}(pk)$ . Each coefficient of the vector of polynomials is 13 bits, and we save the pk in coefficient format one by one. Once a minimum of 64 bits is stored, those bits are used for absorption while new coefficients are introduced in the buffer. The ASCON absorb's input block size is 64 bits (determined by ASCON rate). We load the first 5 coefficients of pk (65 bits) to the shift register for the first absorb. The input block of the first absorb step consists of the first 4 coefficients and 12 bits from the least significant bits (LSB) of the 5th coefficient. One bit of the 5th coefficient remains in the shift register. Then, we load the next 5 coefficients of the pk to the shift register. Now, the shift register holds 66 bits of input. We use 64 bits from the LSB (including the remaining 1 bit of the 1st 5 coefficients) as the second input block. This process continues until the whole pk is absorbed.

Figure 9: Structure of ASCON XOF hardware

Figure 10: Memory organization of the NTT module

As the greatest common divisor between 13 and 64 is 1, the minimum size of the shift register needs to be 64+12=76 to accommodate extra bits of the input stream for all possible cases.

The same buffer temporarily stores the output blocks when the ASCON block works in PRF mode, producing the public matrix  $\hat{A}$ . ASCON squeeze generates 64-bit output after a 12 round permutation  $p^{12}$ , and each coefficient size of A is 13 bits. Then, these coefficients are fed to the rejection sampler. It accepts if the coefficients are less than q. So, only four coefficients can be constructed after a single squeeze. There will be 12 bits remaining in the shift register. After the next squeeze, another 64 bits output is added to the shift register. To accommodate all the bits, the same 76-bit shift register is used. From these 76 bits, 65 bits from the LSB are utilized to construct the next 5 coefficients of the matrix  $\hat{A}$ , and 11 bits will remain in the shift register. This process will continue until the whole matrix is generated.

The ASCON block is required to sample the secret s (or s') and error e (or e', e''). The pseudorandom bits created by ASCON permutation are fed to the CBD sampler to construct the final secret and error coefficients. Here, the 16 bytes seed +1 byte nonce<sup>2</sup> works as the input of the absorb step. Three absorb steps are required as the input block size is 64 bits. To construct a coefficient of the secret or error, 4 bits of XOF output are needed. Therefore, 4-times squeeze is required to generate a single polynomial.

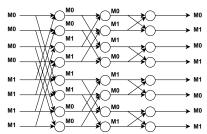

# 4.4 Memory organization

One of the key design aspects of our design is to reduce memory as much as possible to make it resource-constraint-device friendly. We took two key approaches to achieve this. First, we reduce total memory by carefully choosing the generation of lattice  $\hat{\boldsymbol{A}}$  and secret  $\boldsymbol{s}$ . Second, NTT memory organization is done carefully to accommodate the minimum BRAM usage for NTT.

We use just two 18K BRAMs for NTT/INTT operations and one 18K BRAM for run-time lattice generation and public key storage. While we generate  $\hat{A}$ , the careful design choice of 64-point polynomials gives us the perfect opportunity to synchronize ASCON-XOF-Based  $\vec{A}$  generation and NTT(s) operation. For example, generation of  $\vec{A}$  (13.64 bit) consumes 192 (=3.12 for absorb + 13.12 for squeeze) cycles. However, we often need to squeeze more to accommodate more coefficients, as some are rejected. This takes 12-24 cycles more on average. Our NTT is a single butterfly design; hence, NTT( $\boldsymbol{s}$ ) takes 32.6 = 192 cycles. This careful design ensures that both hardware components work synchronously. This also gives us the perfect opportunity for a runtime secret generation, which may not be preferred for NIST standard Kyber as NTT takes significantly more cycles for Kyber. As we need to generate lattice A, NTT(s) can be done within that time. This ensures that we can store the secret seeds and generate them every time, reducing the memory requirement for the secret by a significant amount. For example, we need to keep storage of 1 polynomial generation related to the secret generation contrary to 1 vector of a polynomial of the most optimized Kyber design [NIS23b]. If we choose 128-/256-point NTT, NTT(s) takes more cycles, causing run time secret generation to be infeasible. We also use trivial ML-KEM optimization [NIS23b], such as run-time A generation. We have a separate memory for the public key. However, that

<sup>&</sup>lt;sup>2</sup>The nonce is specific to each of the polynomials, and its value depends on its index. For example, this extra byte for  $\mathbf{s}_0$  is 0, for  $\mathbf{s}_8$  is 8, for  $\mathbf{e}_0$  is 9, and for  $\mathbf{e}_8$  is 17. Two extra bytes are used to generate the polynomial of matrix  $\hat{\mathbf{A}}$ ; one indicates the column number, and the other is the row number. This method helps to reduce bookkeeping hazards and reduce memory consumption.

is not necessary if it is integrated with IoT devices. IoT devices often have extra memory, which can be utilized to communicate with another party.

NTT memory is implemented with 2 separate memory as shown in Fig. 10. Once the secret is generated, 1st half is written in one BRAM, say M0, whereas 2nd half is written in M1 as coeff[0], and coeff[32] is required in the first stage. At every level, writing is swapped to ensure the next stage data is available from 2 different memory. This strategy ensures streamlined dataflow even with a single port write-enabled memory. We are using 3, 18K BRAMs for this implementation. However, total memory is not used. For example, M0 & M1 need just  $32 \cdot 13$ -bit memory each (416 bit, 2.3% of 18K memory).

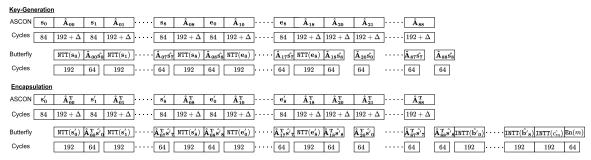

# 4.5 Scheduling