Category:NAND gates

Jump to navigation

Jump to search

inverse of the AND gate, outputs if both inputs are not on simultaneously | |||||

| Upload media | |||||

| Subclass of | |||||

|---|---|---|---|---|---|

| |||||

Subcategories

This category has the following 38 subcategories, out of 38 total.

4

- 4011 (CMOS) (32 F)

- 4012 (CMOS) (6 F)

- 4023 (CMOS) (9 F)

- 4068 (CMOS) (2 F)

- 4093 (CMOS) (5 F)

7

C

- CMOS NAND gates (13 F)

D

- DTL NAND gates (7 F)

N

- NMOS NAND gates (6 F)

S

- NAND gate symbols (57 F)

T

- TTL NAND gates (13 F)

Media in category "NAND gates"

The following 85 files are in this category, out of 85 total.

-

155ЛА18 Планета.jpg 719 × 524; 108 KB

-

2. Teorema.png 620 × 166; 5 KB

-

2. Theorem.svg 512 × 91; 1 KB

-

2014-01-15 08-38-50 electronique-site-plutons porte-logique.jpg 3,465 × 1,320; 1.92 MB

-

3 NAND gates with 2 variables.svg 300 × 160; 5 KB

-

3И-НЕ 74LS(К555).JPG 236 × 195; 21 KB

-

3И-НЕ 74LS(К555).svg 642 × 520; 29 KB

-

4phase.jpg 583 × 268; 39 KB

-

7400 Circuit.svg 319 × 372; 34 KB

-

74LS00 Circuit.svg 319 × 372; 35 KB

-

74LS00 Übertragungskennlinie.svg 340 × 283; 9 KB

-

AND by NAND jp.svg 700 × 100; 14 KB

-

And feito com a porta NAND.jpg 729 × 279; 35 KB

-

Bascule JK.svg 512 × 361; 25 KB

-

CMOS NAND Layout2-ru.svg 297 × 585; 19 KB

-

Constructing NAND gate from NOR gates.png 258 × 127; 3 KB

-

Constructing NOR gate from NAND gates.png 258 × 127; 3 KB

-

Contact-nand.png 226 × 74; 2 KB

-

CPU NAND2.PNG 400 × 250; 6 KB

-

Crossover nand svg.svg 478 × 230; 38 KB

-

Crossover nand.pdf 795 × 383; 22 KB

-

DeMorgan Logic Circuit diagram DIN.svg 1,300 × 900; 14 KB

-

Digitale Kreuzschaltung 1.png 1,100 × 1,400; 40 KB

-

Dlnand.svg 801 × 1,173; 11 KB

-

FWE U107D.jpg 1,800 × 1,660; 215 KB

-

High Threshold Logic circuit diagram.jpg 525 × 416; 35 KB

-

IMPLY gate NAND.png 291 × 120; 4 KB

-

Impulse NAND.svg 1,100 × 900; 7 KB

-

Inversor feito com a porta NAND.jpg 678 × 313; 33 KB

-

ISO-RS-FF-NAND-with-clock.png 882 × 600; 8 KB

-

ISO-RS-FF-NAND-with-clock.svg 347 × 174; 17 KB

-

JK-FlipFlop (4-NAND).PNG 900 × 500; 32 KB

-

Logik-nand.svg 347 × 222; 12 KB

-

Logische Verknuepfung NAND.svg 2,000 × 1,200; 87 KB

-

MC849 Circuit.svg 337 × 351; 31 KB

-

MFrey Not A NAnd Not B.svg 150 × 80; 17 KB

-

MFrey Task 1 Solution NAND 2 Input.svg 640 × 480; 62 KB

-

MFrey Task 1 Solution NAND-small.svg 300 × 300; 51 KB

-

MFrey Task 1 Solution NAND.svg 640 × 480; 53 KB

-

NAND ANSI.svg 100 × 50; 481 bytes

-

NAND en schéma électrique.svg 326 × 102; 8 KB

-

NAND from NOR.svg 280 × 100; 20 KB

-

NAND Gated SR Latch.png 1,280 × 771; 42 KB

-

NAND logic circuit jp.svg 400 × 100; 15 KB

-

NAND-poort kontakt equivalent.png 218 × 91; 670 bytes

-

NAND-poort relais.png 218 × 194; 2 KB

-

NAND-switch-2.png 800 × 534; 22 KB

-

NAND-switch.PNG 190 × 129; 2 KB

-

NOR from NAND.svg 280 × 100; 22 KB

-

NOR NAND.PNG 175 × 69; 1 KB

-

NOT by NAND jp.svg 450 × 100; 10 KB

-

OR by NAND jp.svg 700 × 200; 19 KB

-

Or feito com a porta NAND.jpg 737 × 360; 45 KB

-

OR from NAND.svg 200 × 100; 19 KB

-

OU-exclusif-nand.png 1,257 × 689; 2 KB

-

Phase detectors.svg 531 × 478; 135 KB

-

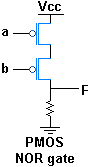

PMOS NOR corr.png 89 × 167; 1 KB

-

PMOS-NAND-gate.svg 461 × 673; 24 KB

-

Puerta lógica NAND biología sintética.png 1,065 × 236; 72 KB

-

Puerta NAND con transistores.jpg 299 × 387; 8 KB

-

Relay nand.svg 200 × 150; 11 KB

-

RS-FF-in-NAND.png 600 × 643; 5 KB

-

RTL npn nand.png 234 × 205; 3 KB

-

Schema NAND poort.jpg 886 × 372; 55 KB

-

Simplified NAND gate circuit using 2 transistors.svg 320 × 420; 6 KB

-

Skakelaar NAND.jpg 170 × 107; 3 KB

-

SR Flip-flop Diagram.svg 200 × 125; 18 KB

-

SR Latch with 4NANDs.svg 294 × 177; 24 KB

-

Switch NAND.jpg 170 × 107; 4 KB

-

Switch NAND.svg 283 × 142; 2 KB

-

SynBioCirc-NandLogicGate.jpg 1,065 × 236; 112 KB

-

Tabela Verdade Porta NAND.jpg 126 × 173; 9 KB

-

Transistor fault in a CMOS NAND gate.png 551 × 592; 19 KB

-

TTL npn nand.png 241 × 220; 4 KB

-

Tungsram 75450APC.jpg 2,307 × 1,181; 1.1 MB

-

USpatent3356858 fig6.png 1,208 × 993; 87 KB

-

Venn-NAND-static.png 1,032 × 396; 195 KB

-

Venn-NAND.gif 480 × 304; 4.84 MB

-

XNOR from NAND 2.svg 320 × 150; 14 KB

-

XNOR from NAND.svg 380 × 100; 25 KB

-

XOR from NAND 2.svg 330 × 150; 14 KB

-

XOR from NAND.svg 300 × 100; 22 KB

-

XOR Using NAND.jpg 303 × 120; 31 KB

-

XOR using NAND.svg 248 × 76; 14 KB