# A Single Phase Latch for High Speed GaAs Domino Circuits

S. Nooshabadi School of Engineering University of Tasmania Hobart TAS 7001, Australia saeid@cs.ntu.edu.au J. A. Montiel-Nelson, A. Núñez, R. Sarmiento & J. Sosa Research Institute for Applied Microelectronics Univ. of Las Palmas de Gran Canaria 35017 Las Palmas de Gran Canaria, Spain montiel@cma.ulpgc.es

### Abstract

A Single Phase Latch (SPL) suitable for GaAs domino logic gates and compatible with DCFL is presented. Two versions of the SPL are reported in this work: Single Ended SPL used in pure domino logic and Differential SPL used in dynamic Cascode Voltage Switch Logic. SPL is compared with other common GaAs dynamic circuits and latches. The results demonstrate that SPL is superior in terms of device count, area, clock rate and power consumption.

## 1. Single Phase Latch (SPL) Design

Pipelining dynamic logic circuits provides full use of the clock period. In typical dynamic design [1], one half of the clock cycle is used for a precharging and the other half for the logic evaluation, so that when parts of the circuit evaluate the other parts precharge and vice–versa.

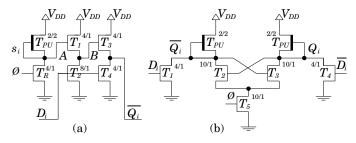

Circuit diagrams for a Singled Ended and Differential SPL are shown in Figure 1(a) and (b). They were designed for implementation in a 0.6  $\mu$ m E/D process (H–GaAsIII) from Vitesse.

### 2. Performance Comparison

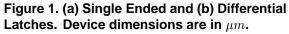

Table 1 compares the performance of SPL in relation to the best performance reported dynamic latch for high speed GaAs domino circuits and static latch work. As can be observed SPL has the best performance in terms of operation frequency, chip area, device count and power dissipation.

Differential SPL provides an alternative to latch CVSL reducing the number of devices with less power consumption and operation frequency, and a marginal degradation in performance is illustrated.

#### 3. Acknowledgement

The support provided by the Spanish Interministerial Commission of Sciencie and Technology (CICYT) under DSIPS (TIC97–0953) project and Australian Research Council are greatly acknowledge.

#### References

- J. A. Montiel-Nelson, and S. Nooshabadi, "High Speed GaAs Subsystem Design using Feed Through Logic", in *Proc. of Design Automation and Test in Europe*, pp. 509–513, March 1999.

- [2] Vitesse Semiconductor Corporation, "ASIC Designer's Reference Library", FX/VIPER Gate Array Macrocell Libraries, April 1996.

- [3] K. R. Nary and S. I. Long, "Dynamic Latch for High Speed GaAs Domino Circuits", *IEE Electronics Letters*, vol. 28, no. 1, pp. 36–37, January 1992.

| $\texttt{Latch} \rightarrow$    | DCFL  | Dynamic | SPL    |       |

|---------------------------------|-------|---------|--------|-------|

| Perf. $\downarrow$              | [2]   | [3]     | Single | Diff. |

| $\mu m^2$                       | 4500  | 2508    | 1070   | 1605  |

| Devices                         | 12    | 8       | 6      | 7     |

| MHz                             | 750   | 350     | 2000   | 833   |

| mW                              | 2.38  | 0.8     | 0.69   | 0.46  |

| $\frac{\mu m^2 \times mW}{MHz}$ | 14.28 | 5.73    | 0.36   | 0.88  |

#### **Table 1. D-Latches Comparisons**